| 216.73.216.154 , 26405th | 1997/03/19 UPDATED |

Copyright(C)1994 H.Kashima 94/9/21

そこで、ターゲットがメモリをアクセスした直後(/CS)の立ち上がり) から、数十ナノ 秒はターゲットが計算中であるためアクセスが絶対ないと仮定し、エミュレーションメ モリを2ページ用意して、その数十ナノ秒の期間に切換えてしまおうという訳である。 切換えるだけならば、その数十ナノ秒で充分完了できる。

これならば、選択されていない方のページは低速なシステム(セントロI/Fを介したホ スト)からでも容易にアクセスが可能になる。

ホストとのインタフェースにはセントロニクスを使用している。 セントロニクスを使 用する事により、制御用マイコンの搭載を不要とし、コストを抑えることができる。

プリンタポートは出力8ビット, 入力1ビット(PC98の場合)しか無いので、SPREへ のデータ転送はビット単位とし、レジスタ番号2ビット, ビット番号3ビット, ビッ ト情報1ビットの合計6ビットを操作し、4バイトのコントロールレジスタを操作す る。 SPREからのデータ転送はシリアル転送とし、シフトレジスタをコントロールレ ジスタ上のクロック, ロード ビットにて操作し1バイトのデータをリードする。

また、オーバーシフトしてリードする事により、ターゲット電源, カレントページ 値を得ることができる。 また、リセットSWは、全てのレジスタをクリアし、RO Mをセレクトした状態に初期化する。

レジスタは最高 16まで増設できるので、16 BITや 128KB化にも容易に改造できる。

[セントロ入力] ビット 機能(全て反転値) ------------------------------------- bit 0 データビット /d0 bit 1 ビット番号 /b0 bit 2 ビット番号 /b1 bit 3 ビット番号 /b2 bit 4 レジスタ番号 /r0 bit 5 レジスタ番号 /r1 bit 6 未使用 bit 7 未使用 /STR データ書込み(UP edge) BUSY 受信データ [SPRE内部レジスタ] レジスタ番号 機能 ----------------------------------------- 0 アドレス(a0 - a7) 1 アドレス(a8 - a15) 2 データ(d0 - d7) 3 コントロール [レジスタ#3 コントロール] ビット 機能 ------------------------------------------ bit 0 シフトレジスタ クロック(UP edge) bit 1 シフトレジスタ ロード(Lo) bit 2 メモリーライト(UP edge) bit 3 未使用 bit 4 シフタ SER入力. 0: 電源, 1:ページ番号 bit 5 ページ切換えクロック(DOWN edge) bit 6 ROM/RAM切換え 0: ROM, 1: RAM bit 7 ページ番号 0: PAGE#0, 1: PAGE#1

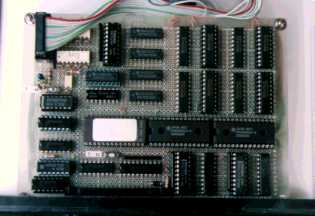

切換え関連のデバイスは遅廷を抑えるため 74AC(T)タイプを使用し、S-RAMも高速タ イプ(80ns) を使用した。 バスバッファなどの遅廷も含めて大体 120nsの ROMに相当 するスピードを得られる。

メモリ切換えは、ターゲットの動作中に切換えるため、全て ターゲットの /CSに 同期して行なう。 ターゲットが絶えず /CSを発行する訳ではないので、ホスト側で 強制切換えができるようにしておく。

パスコン(0.1μF)は IC 2個に1つ以上必ず取り付けること。 当初、パスコンをケチ って付けないで動かしたら、見事に誤動作した。

当初の設計では、セントロ入力はフォトカプラでカップリングしていたが(別添の写真 では TLP521 が付いていますね)、転送速度が遅くなるのと、PC98では SPREからのデー タが受信できないという事もあって、パスした(高速のカプラは高価)。

PC98のプリンタ端子に接続する簡易型 ROMライタの製作/奥村 哲雄氏

kashima@keisei.tsukuba.ac.jp NAG03325 in NIFTY-Serve

![[注意]不適正な題名は即座ゴミ箱、名前を名乗らぬ者への返事はしない事があります。フリー系メールからは自動的に拒絶する場合があります。](/~kashima/maddr2.gif) -- LINK FREE -- |

||

| HOME | LAST |